嗯~從週一開始弄的說,沒想到進度嚴重”超前”,從0%到100%大約20小時就搞定了.快得連小宗宗都大呼不可思議XD (今天的日記可能很悶,因為很多專業的東西)

這次的VHDL專題有兩個選擇,一個是小型16-bit processor(處理器),另一個是老師不太推薦的AES(Advanced Encryption Standard,進階加密標準).小宗宗怎麼看都是覺得AES比較好寫,因為期中的專題是做RC5加密/解密,只要把裡面的加密/解密,key expansion三個區塊換掉就可以,其他的部分通通都可以沿用.

經過一番思考後,便決定先從AES開工看看,反正還有七天的時間,萬一途中苗頭不對還可以緊急跳來改做16-bit processor.第一天開始研讀AES的Standard(FIPS PUB 197),一開始還蠻輕鬆愉快的,不過看到中間時遇到multiplication in GF(28),這玩意就完全搞不懂了.

他好像是多項式的乘法但是又不太一樣,有點像矩陣,但是又好像不是,看得小宗宗一頭霧水,Google一下後好像又和什麼橢圓曲線加密有關,還有什麼Finite field(又稱Galois field),完全沒聽過,只好先跳過XD

不過到接近後段時,忽然又豁然開朗,發現那個乘法加密/解密時只有一個步驟(MixColumns)會用到,其他的步驟都可以用已知的知識去解題.所以小宗宗馬上就開始進行加密方塊的程式編寫,當然最重要的那MixColumns就先跳過啦~後來小宗宗發現網路上有別人寫好的code,所以先把別人的MixColumns程式copy先做測試,完成加密的方塊程式.

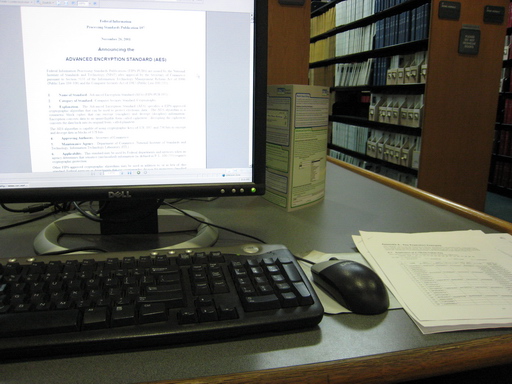

隔天去學校圖書館查到了不少相關的資料的說,小宗宗一直認為圖書館很遜,因為裡面的書都超古的,後來小宗宗發現,其實圖書館最強的地方不是那些積滿灰的古書,而是那幾台電腦啊~圖書館的電腦可以免費連上IEEE查詢Paper,一般來說這項服務是要付費的.小宗宗很快的看了幾篇Paper後,挑了幾篇按了Print鍵,嗯~似乎有感覺了,很快的去邊邊角落找了個桌子坐下來研究一下剛剛印好的文章.看了Key Expansion的解說,一整個豁然開朗啊~Key Expansion也是輕鬆愉快就理解完畢.

圖書館裡查資料,右邊是印出來”疑似”有用的IEEE paper.

馬上滿心期待的極速回家開始進行Key Expansion的程式寫作,很快的就做出來了.但是…進行RTL Synthesis(把程式轉成電路)後,竟然爆掉XD因為吃掉太多資源,光是Key Expansion就吃掉快90%的FPGA空間,那編碼和其他I/O電路百分之兩百燒不進去.這…超打擊…一切全部白費T_T

洗個澡尋找新靈感,嗯~何不試試看把Key Expansion改用On Fly方式產生,也就是說當編碼或解碼到一半,要用到Key的時候再去叫Key Expansion送一份新Key過來.這樣就不用準備一個很大的暫存記憶區來存整個Key(大約是44×4=176bytes).馬上小改一下程式先驗證看看是不是真的是暫存記憶區的問題,把記憶區縮小到10%後重新Synthesis.Ya~只見FPGA的空間瞬間減少大半,看來改用On fly就OK啦~看一看時間五點多,該睡了.

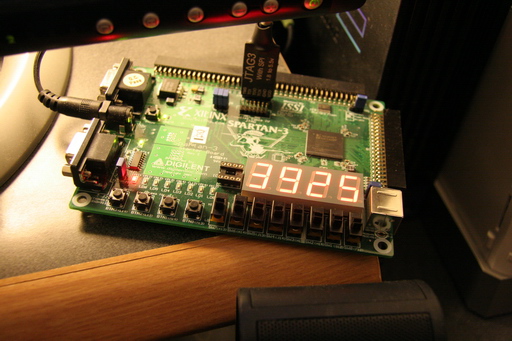

今天下午程式進行大規模修改,最後終於在天黑後沒多久整個燒到FPGA全部測試完畢.後面很意外的沒有遇到很多大問題,小宗宗把整個架構包含I/O一次寫完後才進行測試,很意外的改沒兩次就收工了.和期中專題那次等Synthesis的時間可以看好幾集我猜差很多.這次大概只Synthesis不到五次就完工了,沒啥大問題.嗯~看來又可以優閒打電動打個一兩天了XD

下午做到一個段落,這時才想到沒吃午餐(四點多),趕緊去外頭買個漢堡包~

晚餐是謎一般的假鍋貼(還是味全的喔),超像水餃的說

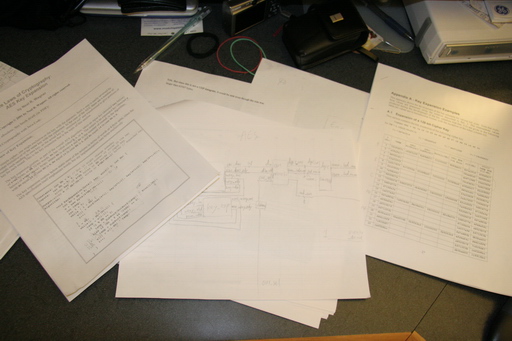

一些手稿和參考資料

燒進FPGA後的完成品

Leave a Comment